❖본 조사 보고서의 견적의뢰 / 샘플 / 구입 / 질문 폼❖

첨단 패키징 시장 규모 및 점유율 분석 – 성장 동향 및 전망 (2026-2031) 보고서 요약

# 1. 시장 개요 및 주요 통계

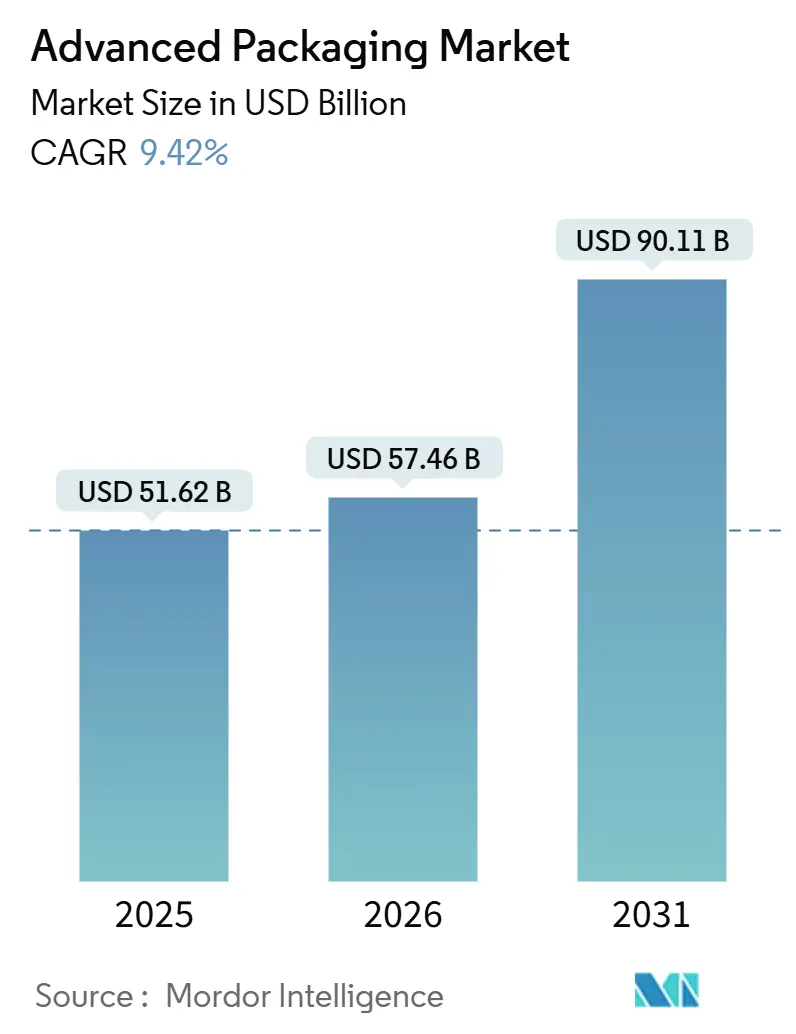

Mordor Intelligence의 보고서에 따르면, 첨단 패키징 시장은 2025년 516.2억 달러에서 2026년 574.6억 달러로 성장하고, 2031년에는 901.1억 달러에 달할 것으로 전망됩니다. 이는 2026년부터 2031년까지 연평균 성장률(CAGR) 9.42%를 기록할 것으로 예상됩니다.

주요 시장 통계:

* 연구 기간: 2020년 – 2031년

* 시장 규모 (2026년): 574.6억 달러

* 시장 규모 (2031년): 901.1억 달러

* 성장률 (2026년 – 2031년): 9.42% CAGR

* 가장 빠르게 성장하는 시장: 중동

* 가장 큰 시장: 아시아 태평양

* 시장 집중도: 중간

* 주요 기업: Amkor Technology, Inc., Taiwan Semiconductor Manufacturing Company Limited, Advanced Semiconductor Engineering Inc., Intel Corporation, JCET Group Co. Ltd (순서 무관)

# 2. 시장 분석 및 주요 동인

첨단 패키징 시장은 기존의 노드 축소(node-shrink) 경제학에서 칩렛(chiplet), 인터포저(interposer), 스택형 다이(stacked-die) 어셈블리를 통해 전력 효율적인 성능을 제공하는 이종 집적화(heterogeneous integration)로 전환되고 있습니다. 이는 기존의 모놀리식(monolithic) 스케일링이 더 이상 경제적으로 지원할 수 없는 한계를 극복하기 위함입니다.

주요 시장 성장 동인:

* AI 및 고성능 컴퓨팅(HPC)을 위한 이종 집적화 수요 증가 (+2.1% CAGR 영향): 칩렛 아키텍처는 고대역폭 인터포저로 연결된 여러 타일에 로직, 메모리, I/O를 분할하여 모놀리식 설계가 전력 한계 내에서 달성할 수 없는 컴퓨팅 밀도를 가능하게 합니다. TSMC의 CoWoS(Chip-on-Wafer-on-Substrate) 및 Intel의 Foveros Direct 하이브리드 본딩 기술은 이러한 추세를 주도하며, 2.5D 및 3D 플랫폼의 두 자릿수 성장을 견인합니다.

* 소비자 기기 소형화로 인한 웨이퍼 레벨 패키징(WLP) 채택 증가 (+1.6% CAGR 영향): 스마트폰 및 웨어러블 기기는 6mm 미만의 Z-높이를 목표로 하며, 팬아웃 웨이퍼 레벨 패키징(Fan-out WLP)은 다이 표면에 I/O를 재분배하여 0.4mm 미만의 패키지 두께를 달성합니다. 애플과 퀄컴이 이미 팬아웃 기술을 채택했으며, 웨어러블 바이오센서는 와이어 본드를 제거하여 충격 저항 및 밀봉성을 향상시키는 팬인 칩 스케일 패키지(Fan-in CSP)를 도입하고 있습니다.

* 정부의 반도체 보조금 정책 (CHIPS 및 EU Chips Act) (+1.8% CAGR 영향): 미국 CHIPS 및 과학법은 첨단 패키징을 전략적 역량으로 명시하며 390억 달러의 직접 보조금과 750억 달러의 대출 보증을 제공합니다. TSMC의 애리조나 공장(66억 달러 보조금)은 2025년부터 CoWoS 생산을 시작할 예정입니다. EU Chips Act는 430억 유로를 지역 파일럿 라인에 투자하며, 한국은 26조 원 규모의 패키지로 삼성 평택 공장의 생산 능력을 40% 확장합니다. 이러한 보조금 경쟁은 공급망을 재편하고 첨단 패키징 시장을 지역 클러스터로 분할하고 있습니다.

* 전기차(EV) 전력 전자 장치의 신뢰성 요구 증대 (+1.5% CAGR 영향): 실리콘 카바이드(SiC) MOSFET 인버터는 200°C 이상의 열 사이클에 직면하며, 15년 차량 수명을 견딜 수 있는 구리 필러(copper-pillar) 및 하이브리드 본드(hybrid-bond) 연결로의 전환을 강제합니다. 인피니언(Infineon)의 CoolSiC 모듈과 테슬라의 하이브리드 본딩 SiC 모듈은 이러한 신뢰성 요구를 충족하며, 자동차 전력 단계에서 첨단 패키징의 핵심 차별화 요소가 되고 있습니다.

* 신흥 글래스 코어 기판을 통한 패널 레벨 패키징 가능성 (+1.2% CAGR 영향): 750mm 정사각형 글래스 기판으로 확장하여 다이 핸들링 비용을 40% 절감할 수 있는 패널 레벨 패키징이 주목받고 있습니다.

* 하이퍼스케일 데이터 센터의 Co-Packaged Optics 수요 (+1.3% CAGR 영향): 데이터 센터의 고성능 요구사항이 Co-Packaged Optics의 채택을 촉진하고 있습니다.

# 3. 시장 성장 제약 요인

* 첨단 패키징 라인의 높은 자본 집약도 (-1.4% CAGR 영향): 패널 레벨 공장은 리소그래피, 전기도금, 테스트 장비 등에 라인당 5억 달러 이상을 요구하며, 투자 회수 기간이 5년을 초과합니다. 하이브리드 본딩 장비는 시간당 30개 웨이퍼 처리 능력에 1,500만 달러 이상으로 생산 병목 현상을 야기합니다. 정부 보조금이 고임금 지역 프로젝트 비용의 30~40%만을 충당하므로, 민간 투자자들은 상당한 자금 격차를 메워야 하며 이는 신규 공장 확장을 지연시킵니다.

* 산업 통합으로 인한 외주 마진 압박 (-1.1% CAGR 영향): 통합 장치 제조업체(IDM)가 칩렛 상호 연결 IP 보호를 위해 패키징을 내재화하면서, 2025년 제3자 물량이 두 자릿수 감소했습니다. 삼성은 I-Cube 패키징을 파운드리 웨이퍼와 번들링하여 고객을 단일 공급업체 생태계에 묶어두고 있습니다. 소규모 OSAT(Outsourced Semiconductor Assembly and Test) 기업들은 차세대 라인에 자금을 조달하는 데 어려움을 겪으며, 2028년까지 생존 가능한 공급업체 수가 10개 미만으로 감소할 위험이 있어 혁신을 저해하고 공급망 위험을 높일 수 있습니다.

* BT-레진 기판 용량 병목 현상 (-0.9% CAGR 영향): BT-레진 기판 공급이 일본과 대만에 집중되어 있어 공급망 병목 현상이 발생할 수 있습니다.

* 첨단 조립 인력 부족 (-0.8% CAGR 영향): 특히 북미와 유럽에서 첨단 조립 기술을 갖춘 인력 부족이 시장 성장을 제약하는 요인으로 작용합니다.

# 4. 세그먼트별 분석

* 패키징 플랫폼별: 플립칩(Flip-Chip)이 2025년 첨단 패키징 시장 점유율의 41.37%를 차지하며 선두를 유지했으나, 패널 레벨 패키징(Panel-Level Packaging)은 2031년까지 9.72%의 CAGR로 가장 빠르게 성장할 것으로 예상됩니다. 플립칩은 솔더 범프 피치 한계로 AI 가속기에서의 미래가 제한적입니다. 팬아웃 웨이퍼 레벨 패키징은 스마트폰 및 웨어러블에서, 팬인 WLP는 비용에 민감한 RF 모듈에서 강세를 보입니다. 임베디드 다이(Embedded-Die)는 자동차 레이더 설계에 진동 허용 오차를 제공하여 주목받고 있습니다.

* 최종 사용자 산업별: 소비자 가전(Consumer Electronics)이 2025년 첨단 패키징 시장의 48.77%를 차지했으나, 스마트폰 교체 주기가 길어지면서 성장세가 둔화되고 있습니다. 자동차 및 전기차(Automotive and EV) 애플리케이션은 2031년까지 10.11%의 CAGR로 모든 산업 중 가장 빠르게 성장할 것으로 전망됩니다. 이는 800볼트 파워트레인으로의 전환과 SiC 모듈에 대한 의존도 증가에 기인합니다. 데이터 센터 및 HPC 수요는 AI 추론 워크로드와 칩렛 기반 GPU, Co-Packaged Optics에 힘입어 견고하게 유지되고 있습니다.

* 장치 아키텍처별: 2D IC가 2025년 출하량의 73.71%를 차지했지만, 3D IC 설계는 2031년까지 9.55%의 CAGR로 성장할 것으로 예상됩니다. 고대역폭 메모리(HBM) 스택은 로직 다이 위에 본딩되어 DRAM 지연 시간을 70% 단축하며, 인텔의 Foveros Direct는 5ns 캐시 지연 시간을 달성합니다. 2.5D 인터포저는 GPU 및 AI 가속기에서 중간 아키텍처로 남아있습니다.

* 상호 연결 기술별: 솔더 범프(Solder Bump)가 2025년 상호 연결 매출의 58.92%를 차지했지만, 하이브리드 본딩(Hybrid Bonding)은 2031년까지 10.02% 성장하여 솔더의 선두를 잠식할 것으로 예상됩니다. 구리-구리 하이브리드 본드는 5µm 이하의 피치를 가능하게 하고 저항을 40% 감소시켜 AI 가속기에서 두 자릿수 전력 절감 효과를 제공합니다. 구리 필러는 스마트폰의 미세 피치 솔루션으로 사용되었으나, 이제는 중간급 사용 사례에 주로 적용됩니다.

# 5. 지역별 분석

* 아시아 태평양: 2025년 첨단 패키징 시장의 60.57%를 차지하며 압도적인 선두를 유지했습니다. 대만, 중국, 한국, 말레이시아에 위치한 파운드리, OSAT, 기판 제조업체의 깊은 클러스터가 이를 반영합니다. TSMC의 CoWoS 및 삼성의 I-Cube 생산 확대가 AI 가속기 수요를 충족시키며 지역 지배력을 강화하고 있습니다. 일본의 아지노모토(Ajinomoto) 및 이비덴(Ibiden)이 이끄는 기판 생태계는 첨단 패키징 시장의 견고한 재료 공급망을 뒷받침합니다.

* 북미: CHIPS 및 과학법을 통해 390억 달러의 보조금과 750억 달러의 대출 보증이 국내 첨단 패키징 인프라에 투입되면서 점유율을 회복하고 있습니다. TSMC의 애리조나 캠퍼스는 2025년 CoWoS 생산을 시작하며, 인텔은 뉴멕시코와 오리건에서 Foveros 3D 패키징 라인을 확장하고 있습니다.

* 유럽: 2025년에는 미미한 가치를 기록했지만, EU Chips Act의 430억 유로 부양책으로 2030년까지 지역 반도체 점유율이 두 배로 증가할 것으로 예상됩니다. 독일 프라운호퍼(Fraunhofer)의 패널 레벨 파일럿 라인과 이탈리아 ST마이크로일렉트로닉스(STMicroelectronics)의 조립 시설이 핵심입니다.

* 중동 및 아프리카: 작은 기반을 가지고 있지만, 아랍에미리트와 사우디아라비아가 국부 펀드를 활용하여 신규 팹 및 패키징 공장에 투자하면서 2031년까지 9.61%의 CAGR로 가장 빠르게 성장할 것으로 전망됩니다.

* 남미: 브라질의 Ceitec이 지역 자동차 공급업체를 지원하는 등 테스트 및 레거시 조립에 국한되어 있습니다. 전반적인 지리적 분산은 대만에 대한 과도한 의존도를 줄이려는 고객의 요구를 반영하며, 첨단 패키징 시장을 다지역 중복성으로 이끌고 현장 위치를 경쟁 차별화 요소로 만들고 있습니다.

# 6. 경쟁 환경

첨단 패키징 시장 구조는 중간 정도의 집중도를 보이며, 상위 5개 공급업체(TSMC, 삼성전자, Amkor Technology, ASE Technology, Intel)가 2025년 매출의 약 55%를 차지했습니다. 그러나 20개 이상의 추가 기업이 활발하게 활동하며 구매자 유연성을 유지하고 있습니다. 각 선두 기업은 웨이퍼 제조와 고밀도 인터포저, 팬아웃 또는 하이브리드 본드 역량을 번들링하여 경쟁업체가 쉽게 따라올 수 없는 턴키 서비스에 대한 프리미엄을 확보하고 있습니다.

* 주요 기업 전략: 삼성은 I-Cube 패키징을 파운드리 웨이퍼와 통합하여 고객을 단일 공급업체 경로에 묶어두고 칩렛 IP를 보호합니다. Amkor는 애리조나(자동차) 및 포르투갈(항공우주)과 같은 지리적 확장과 팹리스 설계자를 위한 공동 설계 파트너십을 통해 대응합니다. ASE Technology는 Siliconware 합작 투자와 기판 전문 지식을 결합하여 BT-레진 부족 시 공급을 보장합니다. Powertech Technology 및 JCET Group은 자동차용 플립칩 및 팬아웃 패널 레벨 모듈과 같은 전문 틈새시장을 공략합니다.

* 기술 경쟁: TSMC는 1,200개 이상의 CoWoS 특허를 보유하고 있으며, 인텔은 구리-구리 하이브리드 본딩을 선도하고, 어플라이드 머티리얼즈(Applied Materials)는 2µm 라인-앤-스페이스 해상도를 갖춘 글래스 기판 장비 분야에서 지배적입니다. Ansys 및 Cadence와 같은 스타트업은 멀티 다이 전력 네트워크 및 열 경로를 공동 최적화하는 전자 설계 자동화(EDA) 흐름을 확장하여 틈새 하드웨어 혁신가들의 진입 장벽을 낮추고 있습니다. 경쟁 강도는 자본 규모, 특허 장벽, 생태계 정렬에 달려 있으며, 이 모든 것이 첨단 패키징 시장 내 지속적인 통합을 촉진합니다.

# 7. 최근 산업 동향

* 2026년 1월: TSMC는 AI 가속기용 월 15,000개 웨이퍼 생산 능력을 추가하는 28억 달러 규모의 타이난 CoWoS 생산 능력 확장을 발표했으며, 2026년 3분기 생산을 목표로 합니다.

* 2025년 12월: 삼성전자는 8개의 고대역폭 메모리 스택을 로직 다이 주변에 하이브리드 본딩으로 통합한 I-Cube4의 양산을 시작했습니다.

* 2025년 11월: 인텔은 보안 통신용 Foveros 패키징 프로세서를 공급하기 위해 미 국방부로부터 35억 달러 규모의 계약을 수주했습니다.

* 2025년 10월: Amkor는 애리조나 피오리아에 20억 달러 규모의 첨단 패키징 공장을 완공했으며, 실리콘 카바이드 자동차 모듈에 집중할 예정입니다.

이 보고서는 첨단 패키징 시장이 기술 혁신, 최종 사용자 산업의 변화, 그리고 정부 정책의 지원을 바탕으로 지속적인 성장을 이룰 것이며, 특히 이종 집적화 및 고신뢰성 애플리케이션 분야에서 중요한 역할을 할 것임을 시사합니다.

본 보고서는 첨단 패키징 시장에 대한 포괄적인 분석을 제공합니다. 첨단 패키징은 전통적인 집적회로(IC) 패키징 이전에 여러 부품을 통합하고 상호 연결하는 기술로, 전기, 기계, 반도체 등 다양한 구성 요소를 단일 전자 장치로 결합하는 것을 가능하게 합니다. 이는 반도체 제조 시설의 공정 및 기술을 활용하는 것이 특징입니다.

시장 규모 및 성장 전망에 따르면, 첨단 패키징 시장은 2031년까지 901.1억 달러(USD 90.11 billion)에 이를 것으로 예상되며, 2026년부터 2031년까지 연평균 9.42%의 견고한 성장률을 보일 전망입니다.

주요 시장 성장 동력으로는 다음과 같은 요인들이 있습니다:

* AI 및 고성능 컴퓨팅(HPC)을 위한 이종 통합(Heterogeneous Integration) 수요 증가

* 소비자 기기 소형화에 따른 WLP(Wafer-Level Packaging) 채택 확대

* CHIPS Act 및 EU Chips Act와 같은 정부의 반도체 보조금 정책

* 전기차(EV) 전력 전자 장치의 신뢰성 요구 증대

* 패널 레벨 패키징(PLP)을 가능하게 하는 신흥 글라스 코어 기판 기술

* 하이퍼스케일 데이터 센터의 Co-Packaged Optics 수요

반면, 시장 성장을 저해하는 주요 제약 요인으로는 첨단 패키징 라인의 높은 자본 집약도, 산업 통합으로 인한 외주(OSAT) 마진 압박, BT-레진 기판의 공급 병목 현상, 그리고 첨단 조립 분야의 숙련된 인력 부족 등이 지적됩니다. 특히, 패널 레벨 라인당 5억 달러 이상의 높은 자본 투자와 빠른 감가상각은 소규모 OSAT 기업의 진입을 어렵게 하고 있습니다.

보고서는 시장을 다양한 기준으로 세분화하여 분석합니다.

* 패키징 플랫폼: Flip-Chip, Embedded Die, Fan-in WLP, Fan-out WLP, 2.5D/3D, System-in-Package (SiP), Panel Level Packaging (PLP)

* 최종 사용자 산업: 소비자 가전, 자동차 및 EV, 데이터 센터 및 HPC, 산업 및 IoT, 헬스케어/메드테크, 항공우주 및 방위

* 장치 아키텍처: 2D IC, 2.5D Interposer, 3D IC (TSV/Hybrid-Bond)

* 상호 연결 기술: Solder Bump, Copper Pillar, Hybrid Bond, Micro-bump-less Direct Bond

* 지역: 북미, 남미, 유럽, 아시아 태평양, 중동, 아프리카

지역별 분석에서는 아시아 태평양 지역이 2025년 매출의 60.57%를 차지하며 시장을 주도하고 있으며, 이는 대만, 중국, 한국의 밀집된 제조 생태계 덕분입니다. 최종 사용자 산업 중에서는 자동차 및 EV 부문이 2031년까지 연평균 10.11%로 가장 빠르게 성장할 것으로 예상되는데, 이는 실리콘 카바이드(SiC) 전력 모듈이 구리 필러 및 하이브리드 본딩을 채택하는 추세에 기인합니다.

기술적 측면에서 하이브리드 본딩은 5 µm 이하의 상호 연결 피치를 가능하게 하고 저항을 40% 감소시키며, AI 가속기에서 솔더 범프를 대체하며 연평균 10.02%로 확장되고 있어 매우 중요한 기술로 부상하고 있습니다. 또한, 미국, EU, 한국의 정부 인센티브 프로그램은 국내 콘텐츠와 보조금을 연계하여 전통적인 아시아 허브 외 지역에서도 CoWoS, Foveros, 패널 레벨 라인 구축을 촉진하며 글로벌 공급망을 재편하고 있습니다.

경쟁 환경 분석에서는 시장 집중도, 주요 기업들의 전략적 움직임, 시장 점유율 분석 및 Amkor Technology, TSMC, ASE, Samsung Electronics, Intel 등 주요 26개 기업의 상세 프로필을 포함합니다. 본 보고서는 이러한 심층 분석을 통해 첨단 패키징 시장의 현재와 미래 전망에 대한 귀중한 통찰력을 제공합니다.

1. 서론

- 1.1 연구 가정 및 시장 정의

- 1.2 연구 범위

2. 연구 방법론

3. 요약

4. 시장 환경

- 4.1 시장 개요

- 4.2 시장 동인

- 4.2.1 AI 및 HPC를 위한 이종 통합 수요 증가

- 4.2.2 소비자 기기 소형화로 WLP 채택 증가

- 4.2.3 정부 반도체 보조금 (예: CHIPS 및 EU Chips 법안)

- 4.2.4 EV 전력 전자 장치 신뢰성 요구 사항

- 4.2.5 패널 레벨 패키징을 가능하게 하는 신흥 유리 코어 기판

- 4.2.6 하이퍼스케일 데이터 센터의 코패키징 광학 수요

- 4.3 시장 제약

- 4.3.1 첨단 패키징 라인의 높은 자본 집약도

- 4.3.2 산업 통합으로 인한 아웃소싱 마진 압박

- 4.3.3 BT-레진 기판 용량 병목 현상

- 4.3.4 첨단 조립 인력 부족

- 4.4 가치 사슬 분석

- 4.5 규제 환경

- 4.6 기술 전망

- 4.7 포터의 5가지 경쟁 요인

- 4.7.1 공급업체의 교섭력

- 4.7.2 구매자의 교섭력

- 4.7.3 신규 진입자의 위협

- 4.7.4 대체재의 위협

- 4.7.5 경쟁 강도

5. 시장 규모 및 성장 예측 (가치)

- 5.1 패키징 플랫폼별

- 5.1.1 플립칩

- 5.1.2 임베디드 다이

- 5.1.3 팬인 WLP

- 5.1.4 팬아웃 WLP

- 5.1.5 2.5D / 3D

- 5.1.6 시스템 인 패키지 (SiP)

- 5.1.7 패널 레벨 패키징 (PLP)

- 5.2 최종 사용자 산업별

- 5.2.1 가전제품

- 5.2.2 자동차 및 EV

- 5.2.3 데이터 센터 및 HPC

- 5.2.4 산업 및 IoT

- 5.2.5 헬스케어 / 메드테크

- 5.2.6 항공우주 및 방위

- 5.3 장치 아키텍처별

- 5.3.1 2D IC

- 5.3.2 2.5D 인터포저

- 5.3.3 3D IC (TSV / 하이브리드 본드)

- 5.4 상호 연결 기술별

- 5.4.1 솔더 범프

- 5.4.2 구리 필러

- 5.4.3 하이브리드 본드

- 5.4.4 마이크로 범프리스 직접 본드

- 5.5 지역별

- 5.5.1 북미

- 5.5.1.1 미국

- 5.5.1.2 캐나다

- 5.5.1.3 멕시코

- 5.5.2 남미

- 5.5.2.1 브라질

- 5.5.2.2 아르헨티나

- 5.5.2.3 남미 기타 지역

- 5.5.3 유럽

- 5.5.3.1 독일

- 5.5.3.2 영국

- 5.5.3.3 프랑스

- 5.5.3.4 이탈리아

- 5.5.3.5 스페인

- 5.5.3.6 유럽 기타 지역

- 5.5.4 아시아 태평양

- 5.5.4.1 중국

- 5.5.4.2 인도

- 5.5.4.3 일본

- 5.5.4.4 대한민국

- 5.5.4.5 호주

- 5.5.4.6 아시아 태평양 기타 지역

- 5.5.5 중동

- 5.5.5.1 아랍에미리트

- 5.5.5.2 사우디아라비아

- 5.5.5.3 중동 기타 지역

- 5.5.6 아프리카

- 5.5.6.1 남아프리카 공화국

- 5.5.6.2 이집트

- 5.5.6.3 아프리카 기타 지역

6. 경쟁 환경

- 6.1 시장 집중도

- 6.2 전략적 움직임

- 6.3 시장 점유율 분석

- 6.4 기업 프로필 (글로벌 수준 개요, 시장 수준 개요, 핵심 부문, 재무 정보(사용 가능한 경우), 전략 정보, 주요 기업의 시장 순위/점유율, 제품 및 서비스, 최근 개발 포함)

- 6.4.1 Amkor Technology Inc.

- 6.4.2 Taiwan Semiconductor Manufacturing Company Limited

- 6.4.3 Advanced Semiconductor Engineering Inc.

- 6.4.4 JCET Group Co. Ltd.

- 6.4.5 Samsung Electronics Co. Ltd.

- 6.4.6 Intel Corporation

- 6.4.7 Chipbond Technology Corporation

- 6.4.8 ChipMOS Technologies Inc.

- 6.4.9 Powertech Technology Inc.

- 6.4.10 TongFu Microelectronics Co. Ltd.

- 6.4.11 Nepes Corporation

- 6.4.12 STATS ChipPAC Pte. Ltd.

- 6.4.13 Siliconware Precision Industries Co. Ltd.

- 6.4.14 UTAC Holdings Ltd.

- 6.4.15 Walton Advanced Engineering Inc.

- 6.4.16 Xintec Inc.

- 6.4.17 Tianshui Huatian Technology Co. Ltd.

- 6.4.18 King Yuan Electronics Co. Ltd.

- 6.4.19 GlobalFoundries Inc.

- 6.4.20 Semiconductor Manufacturing International Corporation

- 6.4.21 SFA Semicon Co. Ltd.

- 6.4.22 Nantong Fujitsu Microelectronics Co. Ltd.

- 6.4.23 Hana Micron Inc.

- 6.4.24 Unisem (M) Berhad

- 6.4.25 Deca Technologies Inc.

- 6.4.26 Veeco Instruments Inc.

7. 시장 기회 및 미래 전망

❖본 조사 보고서에 관한 문의는 여기로 연락주세요.❖

첨단 패키징은 반도체 칩을 외부 환경으로부터 보호하고, 전력을 공급하며, 외부 회로와 전기적으로 연결하는 전통적인 패키징의 기능을 넘어, 칩의 성능, 전력 효율, 소형화, 다기능화를 극대화하기 위한 혁신적인 기술을 총칭합니다. 이는 무어의 법칙(Moore's Law)의 물리적 한계에 직면하면서, 트랜지스터의 미세화만으로는 더 이상 성능 향상을 달성하기 어려워짐에 따라, 패키징 기술을 통해 시스템 수준의 성능을 향상시키는 '모어 댄 무어(More than Moore)' 전략의 핵심 동력으로 부상하고 있습니다. 첨단 패키징은 여러 개의 이종 칩(heterogeneous chips)을 하나의 패키지 안에 통합하여 시스템 온 패키지(System-in-Package, SiP)를 구현하거나, 칩 간의 연결 거리를 최소화하여 데이터 전송 속도를 높이고 전력 소모를 줄이는 데 기여합니다.

이러한 첨단 패키징은 크게 몇 가지 유형으로 분류될 수 있습니다. 첫째, 2.5D 패키징은 실리콘 인터포저(interposer) 또는 유기 인터포저 위에 여러 개의 칩을 수평으로 배열하고, 이를 통해 칩 간의 고밀도 상호 연결을 구현하는 방식입니다. 고대역폭 메모리(HBM)와 GPU/CPU의 통합에 주로 활용되어 데이터 처리량을 획기적으로 늘립니다. 둘째, 3D 패키징은 TSV(Through-Silicon Via) 기술을 활용하여 여러 개의 칩을 수직으로 적층하는 방식입니다. 이는 패키지 면적을 최소화하고 칩 간의 연결 길이를 극단적으로 줄여 전력 효율과 성능을 동시에 향상시킵니다. 3D 낸드(NAND) 플래시 메모리나 HBM이 대표적인 예시입니다. 셋째, 팬아웃 웨이퍼 레벨 패키징(Fan-Out Wafer Level Packaging, FOWLP)은 웨이퍼 상태에서 칩을 재배치하여 I/O(Input/Output) 패드의 밀도를 높이고, 별도의 기판 없이 패키지를 형성하여 소형화와 성능 향상을 동시에 달성합니다. 마지막으로, 시스템 인 패키지(SiP)는 로직 칩, 메모리, RF(Radio Frequency) 칩, 센서 등 다양한 기능을 가진 이종 칩들을 하나의 패키지 안에 통합하여 시스템 전체의 기능을 구현하는 방식으로, 2.5D, 3D, FOWLP 등 다양한 첨단 패키징 기술이 복합적으로 적용될 수 있습니다. 최근에는 여러 공급업체의 전문화된 칩렛(chiplet)을 통합하는 칩렛 통합 기술도 첨단 패키징의 중요한 한 축을 형성하고 있습니다.

첨단 패키징 기술은 다양한 산업 분야에서 핵심적인 역할을 수행하고 있습니다. 고성능 컴퓨팅(HPC) 분야에서는 인공지능(AI) 가속기, 데이터 센터 서버, GPU 등에 2.5D 및 3D 패키징이 적용되어 방대한 데이터를 빠르게 처리하고 학습하는 데 필수적입니다. 모바일 기기 및 웨어러블 기기에서는 SiP 기술을 통해 제한된 공간 안에 더 많은 기능을 집적하고 전력 효율을 높여 배터리 수명을 연장하며 기기 소형화를 가능하게 합니다. 자율주행차 및 전장 분야에서는 높은 신뢰성과 극한 환경에서의 동작 안정성을 요구하며, 첨단 패키징은 ADAS(첨단 운전자 보조 시스템) 및 인포테인먼트 시스템의 핵심 부품에 적용됩니다. 또한, 5G 통신 장비, 사물 인터넷(IoT) 기기, 의료 기기 등에서도 고성능, 저전력, 소형화 요구를 충족시키기 위해 첨단 패키징 기술이 광범위하게 활용되고 있습니다.

첨단 패키징의 발전을 위해서는 다양한 관련 기술의 동반 성장이 필수적입니다. 먼저, TSV, 마이크로 범프(micro-bump), 하이브리드 본딩(hybrid bonding)과 같은 고밀도 상호 연결 기술은 칩 간의 미세 피치 연결을 가능하게 하여 데이터 전송 효율을 극대화합니다. 또한, 웨이퍼 씬닝(thinning), 다이싱(dicing), 본딩(bonding), 몰딩(molding) 등 정밀한 제조 공정 기술과 함께, 재배선층(RDL, Redistribution Layer) 형성 기술이 중요합니다. 열 관리 및 전력 효율을 위한 첨단 소재 기술, 예를 들어 고성능 기판, 열전도성 소재, 저유전율 소재 등의 개발도 필수적입니다. 패키지 설계 및 시뮬레이션 기술은 칩과 패키지 간의 공동 설계(co-design)를 통해 열, 전기적 특성, 신호 무결성 등을 사전에 분석하여 최적의 패키지 구조를 구현하는 데 기여합니다. 마지막으로, 복잡한 첨단 패키지의 신뢰성을 보장하기 위한 정밀 테스트 및 검사 기술 또한 중요한 관련 기술입니다.

첨단 패키징 시장은 최근 몇 년간 급격한 성장을 이루었으며, 앞으로도 이러한 추세는 지속될 것으로 전망됩니다. 이는 전통적인 반도체 미세 공정의 한계에 도달하면서, 성능 향상의 돌파구를 패키징에서 찾으려는 산업 전반의 움직임 때문입니다. 인공지능, 빅데이터, 5G, 자율주행 등 고성능, 고대역폭, 저전력, 저지연을 요구하는 신기술의 확산은 첨단 패키징 수요를 더욱 증대시키고 있습니다. 특히, 이종 집적(heterogeneous integration)을 통해 다양한 기능을 가진 칩들을 효율적으로 통합하려는 요구가 커지면서, 첨단 패키징은 시스템 전체의 가치를 높이는 핵심 기술로 자리매김하고 있습니다. 또한, 글로벌 공급망의 안정성 확보와 특정 국가에 대한 의존도를 줄이려는 노력의 일환으로 칩렛 기반의 모듈형 설계 및 첨단 패키징 기술의 중요성이 더욱 부각되고 있습니다.

미래 첨단 패키징 기술은 더욱 고도화되고 복잡해질 것으로 예상됩니다. 하이브리드 본딩 기술은 칩 간의 연결 피치를 더욱 미세화하고 직접적인 접합을 통해 성능과 전력 효율을 극대화하는 방향으로 발전할 것입니다. 또한, 패키지 내부에 광학 인터커넥트(optical interconnect)를 통합하여 초고속 데이터 전송을 구현하려는 연구가 활발히 진행되고 있으며, 이는 데이터 센터와 같은 고성능 컴퓨팅 환경에서 병목 현상을 해소하는 데 기여할 것입니다. 시스템 레벨의 통합은 더욱 심화되어, 하나의 패키지 안에 프로세서, 메모리, 센서, RF, 전력 관리 등 모든 기능을 담는 초고집적 SiP가 보편화될 것입니다. 그러나 이러한 발전과 함께 열 관리, 전력 분배, 신호 무결성, 테스트 및 수율 확보, 표준화 문제 등 해결해야 할 과제 또한 산적해 있습니다. 그럼에도 불구하고, 첨단 패키징은 반도체 산업의 지속적인 혁신을 이끌고 새로운 애플리케이션의 등장을 가능하게 하는 핵심 동력으로서 그 중요성이 더욱 커질 것입니다.